If you own an Intel motherboard with a Z170 or Z270 chipset, you might believe that it only supports CPUs up to Intel’s 7th generation, known as Kaby Lake. Even the CPU socket’s pinout …

They’ve been pulling this shit since the early days. Similar tricks were employed in the 486 days to swap out chips, and again in the Celeron days. I think they switched to the slot style intentionally to keep selling chips to a point lol

i dream of a world where the process will cheapen out enough like pcb design, where you can just submit the design you want and they will fab it out for you.

with more players coming into the game because of sanctions, i hope we are now on the path.

Yes, i hope so too, as for now, semiconductor lithography at home is impossible due how big and complex these machines are, so i have same opinion as you are

IIRC, the slot CPU thing was because they wanted to get the cache closer to the processor, but hadn’t integrated it on-die yet. AMD did the same thing with the original Athlon.

On a related note, Intel’s anticompetitive and anti- consumer tactics are why I’ve been buying AMD since the K6-2.

They had integrated the L2 on-die before that already with the Pentium Pro on Socket 8. IIRC the problem was the yields were exceptionally low on those Pentium Pros and it was specifically the cache failing. So every chip that had bad cache they had to discard or bin it as a lower spec part. The slot and SECC form factor allowed them to use separate silicon on a larger node by having the cache still be on-package (the SECC board) instead of on-die.

They’ve been pulling this shit since the early days. Similar tricks were employed in the 486 days to swap out chips, and again in the Celeron days. I think they switched to the slot style intentionally to keep selling chips to a point lol

me when capitalism

thats why we are in dire need of open source hardware.

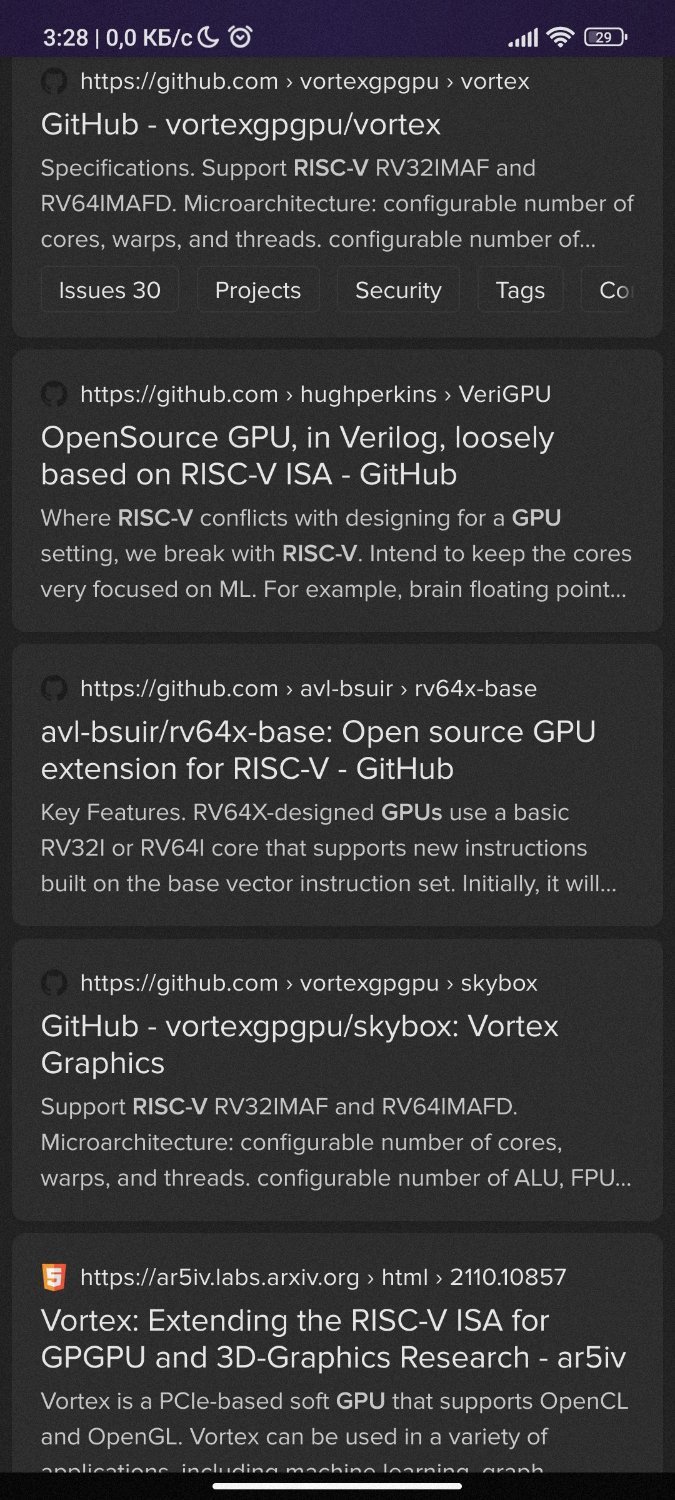

We have open source designs (RISCV also have GPU designs) but we don’t have manufacture power open sourced yet

i dream of a world where the process will cheapen out enough like pcb design, where you can just submit the design you want and they will fab it out for you.

with more players coming into the game because of sanctions, i hope we are now on the path.

Yes, i hope so too, as for now, semiconductor lithography at home is impossible due how big and complex these machines are, so i have same opinion as you are

IIRC, the slot CPU thing was because they wanted to get the cache closer to the processor, but hadn’t integrated it on-die yet. AMD did the same thing with the original Athlon.

On a related note, Intel’s anticompetitive and anti- consumer tactics are why I’ve been buying AMD since the K6-2.

They had integrated the L2 on-die before that already with the Pentium Pro on Socket 8. IIRC the problem was the yields were exceptionally low on those Pentium Pros and it was specifically the cache failing. So every chip that had bad cache they had to discard or bin it as a lower spec part. The slot and SECC form factor allowed them to use separate silicon on a larger node by having the cache still be on-package (the SECC board) instead of on-die.

AMD followed suit for the memory bandwidth part from the K62 architecture. Intel had no reason to do so.

It’s been at least since the “big iron” days.

Technician comes out to upgrade your mainframe and it consists of installing a jumper to enable the extra features. For only a few million dollars.